ПЛИС — интегральные схемы программируемой логики

Логические устройства подразделяются на две категории: фиксированной логики и программируемые. Как следует из названия, устройства с фиксированной логикой выполняют одну (либо набор) функций, которые невозможно изменить после их изготовления. Программируемые устройства также являются стандартными изделиями, которые обладают широким диапазоном логической емкости, скорости переключения, входных и выходных напряжений, и их предназначение может быть изменено в любое время для реализации произвольной функции.

Основные понятия ПЛИС

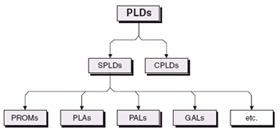

В русскоязычной литературе любую программируемую логику принято называть термином ПЛИС (программируемая логическая интегральная схема). В англоязычной литературе принято различать следующие разновидности программируемых микросхем: PLA, PAL, GAL, SPLD, CPLD, ASIC, FPGA, FPAA, FPID, SoCи т.д.

ПЛИС PLA (Programmable Logic Array)

Программируемые логические интегральные схемы PLA

Программируемые логические интегральные схемы PLA

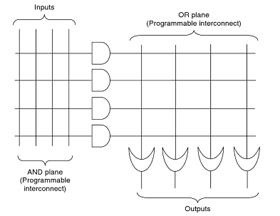

Программируемые логические интегральные схемы наподобие ППЗУ. В данных устройствах оба массива элементов и <И>, и <ИЛИ> являются программируемыми. На рисунке схематично представлен вариант содержащий две программные плоскости <И> и <ИЛИ> имеющие по четыре входа и выхода.

ПЛИС PAL (Programmable Array Logic)

Программируемые логические интегральные схемы PAL

Программируемые логические интегральные схемы PAL

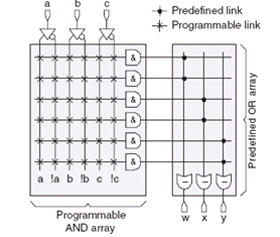

Программируемые логические интегральные схемы наподобие ППЗУ. Однако, в отличие от последних, в данных схемах массив элементов <И> является программируемым, а массив <ИЛИ> - нет. Для примера рассмотрим простую PAL с тремя входами и тремя выходами.

ПЛИС GAL (Generic Array Logic)

Устройства PAL и PLA – однократно программируемые, их конфигурация не может быть изменена; в отличие от них микросхемы GAL основаны на EEPROM и могут реконфигурироваться. Микросхемы GAL были изобретены Lattice Semiconductor. Аналогичные устройства, PEEL (programmable electrically erasable logic), были предложены International CMOS Technology (ICT).

ПЛИС SPLD (Simple Programmable Logic Devices)

В англоязычной литературе микросхемы PROM, PAL, PLA, GAL принято обобщать термином SPLD.

Программируемые логические интегральные схемы SPLD

Программируемые логические интегральные схемы SPLD

ПЛИС CPLD (Complex PLD). Разновидность ПЛИС, содержащая относительно крупные программируемые логические блоки - макроячейки (англ. macrocells), соединённые с внешними выводами и внутренними шинами.

Программируемые логические интегральные схемы CPLD

Программируемые логические интегральные схемы CPLD

Существенный прорыв в разработке ПЛИС произошел в 1984г., когда компания Altera предложила CPLD, применив сочетание CMOS и EPROM технологий. Использование технологии CMOS позволило достичь значительной функциональной плотности и сложности при сравнительно небольшом потреблении энергии, а ячейки (англ. cells) EPROM оказались идеальным средством для использования их при разработке и создании прототипов оборудования.

ПЛИС ASIC (Application Specific IC)

Заказная интегральная схема для решения конкретной задачи. Микросхема способна выполнять ограниченный набор функций с высокой эффективностью. Является своего рода конкурентом ПЛИС. В русскоязычной терминологии - БМК – базовый матричный кристалл, т.е. вентильная матрица с масочным программированием. В англоязычной терминологии ASIC подразделяются на вентильные матрицы, структурированные ASIC, схемы на стандартных элементах и полностью заказные интегральные схемы.

ПЛИС FPGA (Field Programmable Gate Array)

Программируемые логические интегральные схемы FPGA

Программируемые логические интегральные схемы FPGA

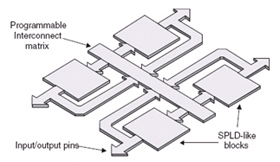

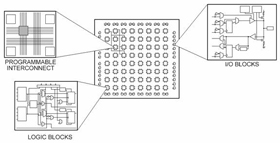

Разновидность ПЛИС, содержащая логические элементы и блоки коммутации. Программа для FPGA хранится в распределённой оперативной памяти микросхемы, поэтому требуется начальный загрузчик.

Примерно к 80-х годам 20 столетия на рынке цифровых микросхем сложилась ситуация, когда возникла ниша между наличием сложных и дорогих в производстве микросхем ASIC и PLD (SPLD и CPLD). Эта ниша заполнилась микросхемами FPGA. Разработчиком FPGA является основатель компании Xilinx Росс Фримен - изобретатель концепции матричного кристалла программируемого пользователем (FPGA).

Развитие архитектур ПЛИС привело к созданию комбинированных структур сочетающих достоинства FPGA и CPLD – например, семейство FLEX (Flexible Logic Element Matrix) от Altera.

ПЛИС FPAA (Field Programmable Analog Array)

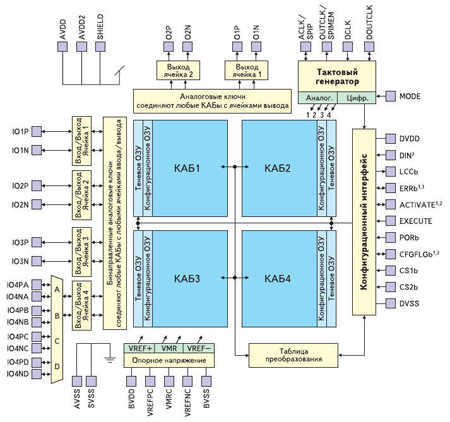

Программируемые логические интегральные схемы FPAA

Программируемые логические интегральные схемы FPAA

Традиционно схемы аналоговой обработки сигналов выполняются на дискретных компонентах. В ряде случаев аналоговая часть занимает значительную площадь печатной платы и требует сложной настройки. Решить проблему создания аналоговых устройств (иногда для определенной полосы частот спектра) позволяет использование программируемых аналоговых микросхем. На настоящий момент крупнейшим производителем таких микросхем является компания Anadigm.

ПЛИС FPID (Field Programmable Interconnect Device)

Эти программируемые логические интегральные схемы содержат программируемые соединения и блоки ввода/вывода, но не содержат логических блоков. Они предназначены для произвольного соединения своих внешних выводов в соответствии с заложенной программой. При отработке прототипов и при создании динамически конфигурируемых систем такие микросхемы весьма полезны. Соединяя ПЛИС через FPIC можно легко варьировать их межсоединения, чего не обеспечивают технологии с жесткой трассировкой (печатные платы и др.).

ПЛИС SoC (System on Chip)

Уменьшение топологических норм проектирования и ряд технологических усовершенствований довели уровень интеграции современных программируемых логических интегральных схем до величин в несколько миллионов эквивалентных вентилей, а быстродействие - до тактовых частот в сотни мегагерц. На таких кристаллах размещают целиком всю цифровую систему (процессор, память, интерфейсы, и др.).

Применение ПЛИС

ПЛИС SPLD

Микросхемы SPLD по-прежнему выпускаются многими производителями. Среди них есть и такие всемирно известные корпорации, как Texas Instruments, NXP, Lattice. У Lattice такие компоненты называются «mature devices», т. е. зрелые, продуманные. Для программирования логических интегральных схем SPLD были разработаны специальные программы (логические компиляторы) для перевода булевых уравнений, таблиц истинности или диаграмм состояний в так называемый файл JEDEC* — закодированный в стандартизированной форме список плавких перемычек, которые следует уничтожить. В дальнейшем, при появлении новых типов ПЛИС, логические компиляторы стали называться языками HDL (Hardware Description Language). На сайте NXP приведены варианты использования компонентов SPLD, в AN036 рассматривается применение микросхемы PLC42VA12 в контроллере расширителя интерфейса I2C.

Компания Altera предлагает несколько вариантов применения CPLD серии MAX V**:

1. ПЛИС CPLD применяется для расширения количества портов ввода/вывода других стандартных устройств.

Применение ПЛИС CPLD для расширения количества портов

Применение ПЛИС CPLD для расширения количества портов

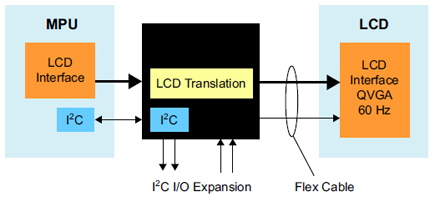

2. Программируемые логические интегральные схемы CPLD применяются для создания мостов (bridge’s) между интерфейсами, т. е. для соединения друг с другом несовместимых по протоколам устройств.

Применение ПЛИС CPLD для создания мостов

Применение ПЛИС CPLD для создания мостов

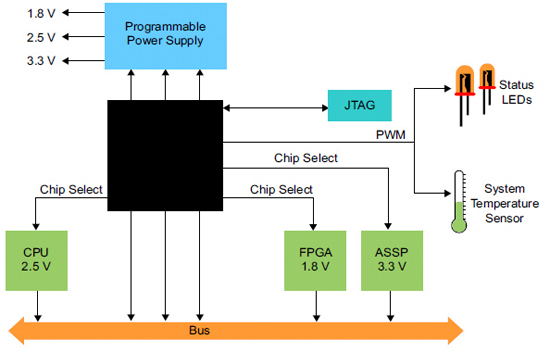

3. Так же ПЛИС CPLD применяется для управления последовательностью включения источников питания и мониторинга других устройств.

Применение ПЛИС CPLD для управления последовательностью включения источников питания

Применение ПЛИС CPLD для управления последовательностью включения источников питания

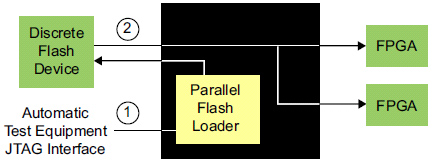

4. Программируемые логические интегральные схемы CPLD могут быть использованы для управления конфигурацией или инициализацией других устройств.

Применение ПЛИС CPLD для управления конфигурацией или инициализацией других устройств

Применение ПЛИС CPLD для управления конфигурацией или инициализацией других устройств

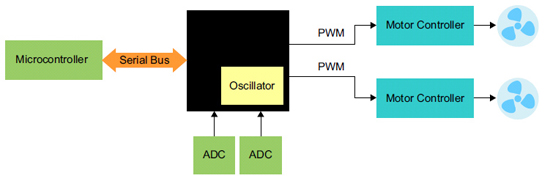

5. ПЛИС CPLD для управления стандартными аналоговыми устройствами в цифровом формате посредством широтно-импульсной модуляции (ШИМ) без применения ЦАП. LUT-архитектура CPLD, выходы с высокой нагрузочной способностью и внутренний генератор микросхемы позволяют обеспечить прямое соединение этой микросхемы с различными стандартными аналоговыми продуктами при использовании ШИМ.

-----------------------------------

*JEDEC Standard JESD3-C, Standard Data Transfer Format Between Data Preparation System and Programmable Logic Device Programmer, June 1994.

**Altera, WP-01146-1.2

Коок Д.А.